# Full-quantum modeling of III-V Tunnel-FETs architectures

# Performance of Nanodevices

Elena Gnani<sup>1</sup>, Michele Visciarelli<sup>2</sup>, Antonio Gnudi<sup>1</sup>, Susanna Reggiani<sup>1</sup>, Giorgio Baccarani<sup>1</sup>

**ABSTRACT.** This paper review the device and circuit performance of co-optimized n- and p-type tunnel field-effect transistors (TFETs) integrated on the same InAs/Al<sub>0.05</sub>Ga<sub>0.95</sub>Sb platform, using a full-quantum ballistic simulator. Based on 3-D full-quantum simulations, the investigated devices feature steep subthreshold slopes and relatively high ON-state currents, and are combined to realize an inverter. Benchmarking against aggressively scaled CMOS logic based on multigate architectures highlights the potential of the proposed TFET implementations to perform up to 10× and 100× faster for  $I_{OFF} = 5$ nA/um and 10 pA/um, respectively, at very low supply voltage  $V_{DD} = 0.25$ V, for equal levels of static power dissipation. Afterwards, a simulation study on the impact of interface traps and strain on the I–V characteristics is carried out, in order to capture the effect of interface/border traps on the device electrostatics. The effect of an experimental  $D_{it}$  distribution of a high-k gate stack on InAs is investigated. Unfortunately, traps induce a significant reduction of the ON-state current. However, it turns out that localized strain at the source/channel heterojunction caused by lattice mismatch is able to induce a performance enhancement for the n-type TFET, with respect to the ideal device, even in the presence of traps. On the contrary, for the p-type one, a current degradation ~ 18% is observed.

**KEYWORDS.** III–V materials, heterojunction, subthreshold slope, interface traps (ITs), quantum transport, strain, tunnel FETs (TFET).

#### 1. Introduction

Aggressive scaling of device dimensions is currently being pursued by multigate field-effect transistors [Auth 12], whereas transistors exploiting different operating principles are required to further reduce the supply voltage V<sub>DD</sub>. Tunnel FETs (TFETs) are considered to be one of the most promising alternatives to the conventional CMOS technology, in the quest for supply voltage reduction and power containment [Lu 14], [Ionescu 11]. TFETs are especially interesting due to their peculiar injection mechanism, that makes it possible to achieve subthreshold swings (SS) lower than 60mV/dec at room temperature and, thus, higher ON-state currents (I<sub>ON</sub>) at very low supply voltages.

Major challenges associated with the TFET architecture include: 1) reaching acceptable  $I_{ON}$  levels; 2) suppressing ambipolar effects, affecting the off-state performance; 3) dealing with the superlinear onset and high saturation voltage of the device output characteristics [Pal 11]; 4) reducing Miller effects associated with the typically high gate—drain capacitance  $C_{gd}$  [Mookerjea 11]; and, 5) cointegrating simultaneously optimized n- and p-type devices. More generally, literature on p-TFETs is relatively scarce compared to that on n-TFETs, and the two device types are often studied separately.

There is wide consensus on the use of III-V based heterostructures with staggered or broken-gap lineups to boost the ON-state current and realize a complementary technology platform, whereas a careful optimization of the device geometry, doping levels, and gate-stack is required to improve performance [Baravelli 14-I]. Furthermore, for digital applications, slope and  $I_{ON}$  are not the only relevant parameters to be considered. Voltage transfer characteristics (VTC), voltage gain and switching current, as well as rise and fall times, contribute to circuit-level performance. In addition, interface states may have a significant impact on the drain current, degrading  $I_{ON}$  and the subthreshold slope [Passlack 10], [Lin 11]. In this respect, the achievement of low interface and border trap densities is one of the main technology challenges to be addressed [Pala 12].

<sup>&</sup>lt;sup>1</sup> Advanced Research Center for Electronic Systems, Department of Electronics, University of Bologna, Italy, elena.gnani@unibo.it, antonio.gnudi@unibo.it, susanna.reggiani@unibo.it, giorgio.baccarani@unibo.it

<sup>&</sup>lt;sup>2</sup> School of Engineering Sciences, KTH Royal Institute of Technology, Kista, Sweden, mvisciar@kth.se

However, for III-V-based TFETs, it is possible to boost the device performance, taking advantage of appropriate strain conditions [Visciarelli 16].

This paper review the device and circuit performance of co-optimized n- and p-type tunnel field-effect transistors (TFETs) integrated on the same InAs/Al<sub>0.05</sub>Ga<sub>0.95</sub>Sb platform. In contrast with the largest part of available literature, a full-band quantum simulation approach is used in this paper to properly account for quantum effects, which strongly influence TFET behavior and, thus, circuit performance. Afterwards, performance of the investigated circuit blocks is compared with best-case predictions for aggressively scaled CMOS logic, based on multi-gate architectures. Afterwards, the investigation is here extended to take into account the combined effect of traps and strain on the device characteristics.

The paper is organized as follows. The physical model used for the investigation is described in Section 2. The TFET-based platform and the proposed inverted implementations are highlighted in Section 3 and 4, respectively. The combined effect of interface traps and localized strain is investigated in Section 5. Concluding remarks are given in Section 6.

## 2. Physical model

Numerical simulations are carried out using a four-band **k•p** Hamiltonian [Vurgafmann 01] in a fully 3-D framework, to accurately model multiband effects and the complex band structure of our devices. A non-equilibrium Green function (NEGF) formalism is employed for transport description within the ballistic approximation [Lake 97], which is expected to be a reasonable assumption for the gate lengths investigated here, due to the high electron mobility and long mean free path of III–V materials. The NEGF module is self-consistently coupled with a 3-D Poisson solver for electrostatics computation.

The effect of strain is included using the Pikus-Bir formalism with Bahder extensions [Bahder 90], [Bahder 93] for zinc-blende crystals. With such an approach, a strain-tensor-dependent matrix Hstrain is added to the basis **k•p** Hamiltonian of the unstrained material. The strain-dependent matrix includes deformation potential constants and k-dependent terms, which couple the different bands with strain among them. Material parameters are taken from [Vurgafmann 01], and spurious solutions in the gap are eliminated using the procedure proposed in [Foreman 01]. Zero wave function penetration in the insulator is assumed. Contact resistances are not considered either, as their impact is strongly dependent on the actual fabrication technology, which is beyond the scope of this paper.

In order to capture the effect of interface/border traps on the device electrostatics, consistently with carrier degeneracy and ballistic transport, the classical Shockley–Read–Hall theory can be properly generalized. The model assumes that traps are of both acceptor and donor type, located at the semiconductor/oxide interface, and uniformly distributed over the interface area. Only the electrostatic effect of traps is considered via Poisson's equation. At every NW cross section, the occupation probability of traps at every energy  $E_t$  in steady state is determined from the balance of electrons and holes emission and capture processes. The electronic states generated by wave function propagation from the source and the drain leads are separately considered, consistently with the ballistic NEGF picture. The derivation of the trap model can be found in [Visciarelli 17-TED].

## 3. Device structure and technology platform assessment

Heterostructures are exploited to achieve satisfactory I<sub>ON</sub> levels with the TFET architecture, and promising experimental studies have been reported on III–V antimonide compounds. Baravelli et al. [Baravelli 14-I] have indicated InAs/Al<sub>0.05</sub>Ga<sub>0.95</sub>Sb as a suitable material pair for cointegration of n- and p-type devices with similar dimensions and opposite choices for the source and channel/drain materials. The TFETs considered here are a modified version of the 7-nm-side platform described in [Baravelli 14-I], and feature a gate length of 20 nm.

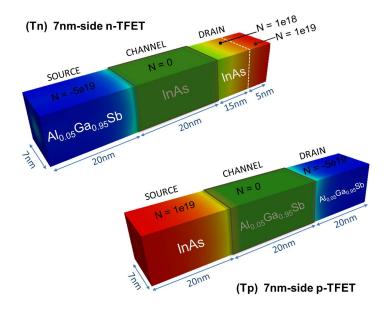

Device sketches are shown in Fig. 1, and feature a gate-all-around nanowire geometry with square cross section.

**Figure 1.** Pictorial view of the n-type (Tn) and p-type (Tp) heterojunction TFETs based on the InAs/Al0.05Ga0.95Sb material pair. Doping concentrations are expressed in cm-3 and abrupt profiles are assumed. A non-uniform drain doping is used to reduce ambipolarity in Tn. The gate dielectric is Al2O3 with an equivalent oxide thickness EOT = 1nm.

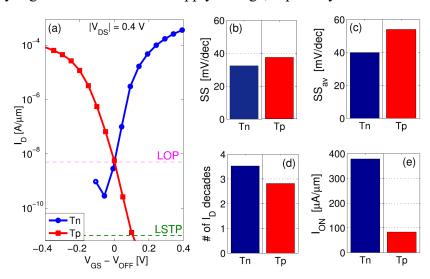

Both devices were designed to meet the International Technology Roadmap for Semiconductors OFF-state current specification of 5 nA/ $\mu$ m at  $V_{DD} = 0.4$  V, with sub-60 mV/decade minimum and average subthreshold slope, together with relatively high ON-currents ( $I_{ON} \sim 350\mu$ A/ $\mu$ m for Tn, and  $I_{ON} \sim 75 \mu$ A/ $\mu$ m for Tp) [Baravelli 14-II]. Turn-on curves computed at  $V_{DD} = 0.4$  V for the TFETs in Fig. 1 are shown in Fig. 2(a), where currents are normalized by the device side. The curves are shifted by the  $V_{GS}$  value ( $V_{OFF}$ ) at which the corresponding  $I_{OFF}$  level is reached, to compare the device performance for equal static power consumption. Both devices exhibit sub-40 mV/decade minimum SS [Fig. 2(b)] and sub-60 mV/decade average subthreshold slopes ( $SS_{av}$ ) [Fig. 2(c)], which are sustained for about three decades of drain current [Fig. 2(d)]. This is combined with relatively high  $I_{ON}$  levels at 0.4 V supply voltage, especially for the n-TFET [Fig. 2(e)].

Figure 2. (a) Simulated  $I_D$ – $V_{GS}$  curves at  $|V_{DS}|$  = 0.4 V for the TFETs in Fig. 1 (normalized by device side for consistency with quantization-induced charge distribution). LSTP (10 pA/ $\mu$ m) and LOP (5 nA/ $\mu$ m) specs on  $I_{OFF}$  are indicated. Curves are shifted by the respective  $V_{OFF}$ , i.e., the  $V_{GS}$  at which  $I_D$  = 5 nA/ $\mu$ m. Corresponding device performance is evaluated in terms of (b) minimum SS, (c) average subthreshold slope, SS<sub>av</sub>, (d) number of current decades over which SS<sub>av</sub> is computed, and (e)  $I_{ON}$  at  $V_{DD}$  = 0.4 V.

It is worth noting that the output curves show a high output conductance at low  $V_{DS}$  for both the n- and p-type devices (see Fig. 4 in [Baravelli 14-II]).

## 4. TFET-based inverter design

This technology platform has been considered as potential competitor of a conventional CMOS logic. The off-current has been fixed at 5 nA/ $\mu$ m and two different supply voltages have been investigated, namely  $V_{DD}$  = 0.4 V and 0.25 V.

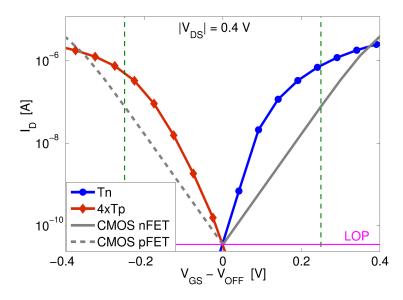

To compensate for the current difference between the n- and p-type devices shown in Fig. 2, four p-type devices connected in parallel are considered. TFETs are benchmarked against FinFET-based CMOS logic projected to the 10-nm technology node. The assumed FinFETs exhibit 14-nm gate length, 9-nm fin width, 21-nm fin height, and are simulated in SPICE using PTM-MG [Sinha 12]. The work functions in PTM model cards are adjusted to make I<sub>OFF</sub> and, thus, static power dissipation, identical for the two device types.

Figure 3. ID–VGS curves of 4×Tp and 1×Tn compared with those of 10-nm-node CMOS FinFETs computed with PTM-MG SPICE models [Sinha 14]. The WFs in PTM model cards are adjusted to make IOFF = 5 nA/µm and, thus, equal static power dissipation. The FinFET subthreshold slope is about 75 mV/decade. Dashed vertical lines: TFET advantage when VDD is reduced from 0.4 to 0.25 V.

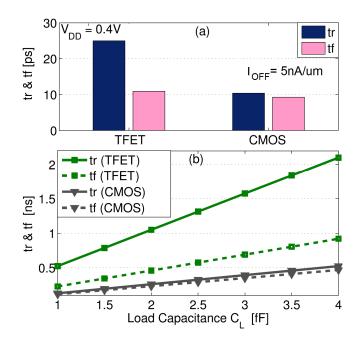

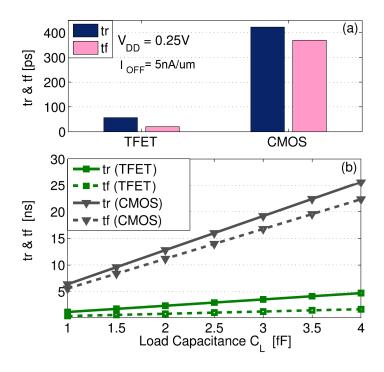

Turn-on curves are compared in Fig. 3 with those obtained from n- and p-type FinFET simulation (4×Tp and 1×Tn). TFETs are seen to provide considerably improved subthreshold performance, and the two architectures exhibit a break-even point for current drive at  $|V_{GS} - V_{OFF}| = 0.35$  V, so that FinFETs have some  $I_{ON}$  advantage at  $V_{DD} = 0.4$  V. As a consequence, CMOS logic is faster than its TFET counterpart, both under self-loading or constant-loading conditions, as demonstrated in Fig. 4 (a) and (b), respectively. Results for the self-loading case are further motivated by the higher effective load of TFET inverters due to the Miller contribution, which is instead assumed to be negligible for the CMOS logic. Under self-loading conditions, an equal inverter stage in a chain configuration is considered. Miller effects are accounted for through an additional load capacitance equal to  $2 \times C_{gd}$ , with the estimated gate-drain capacitance  $C_{gd} \approx 0.8 \times C_g$  (gate capacitance), which is a reasonable assumption for III–V TFETs [Mookerjea 09]. This leads to an effective load of  $2.6 \times C_{in}$  with  $C_{in}$  the total input capacitance. The  $C_{gd}$  component is instead neglected in the constant loading condition. Rise and fall times  $t_{r,f}$  are estimated in response to an instantaneous voltage step, and are computed by integrating the device output characteristics at  $V_{GS} = 0$  V or  $|V_{GS}| = V_{DD}$  [Baravelli 14-II].

**Figure 4.** Rise and fall times of TFET-based inverter and of a 10-nm CMOS-based inverter, operating at  $I_{OFF} = 5 \text{ nA/}\mu\text{m}$ , and  $V_{DD} = 0.4 \text{ V}$ . CMOS logic is faster than TFET in both (a) self-loading and (b) constant loading, because it provides a higher drive current at  $V_{DD} = 0.4 \text{ V}$ , and is not significantly affected by the Miller effect.

On the other hand, Fig. 3 indicates a potential advantage of TFETs at sub-0.35 V supply voltage. More specifically, the advantage in current drive is over  $10\times$  at  $V_{DD}=0.25$  V. As demonstrated in Fig. 5, TFET logic is predicted to be about  $10\times$  and  $7\times$  faster than CMOS logic under self-loading and constant loading conditions, respectively.

Figure 5. Rise and fall times of a TFET-based inverter and of a 10-nm CMOS-based inverter, operating at  $I_{OFF}$  = 5 nA/ $\mu$ m, and  $V_{DD}$  = 0.25 V. TFET logic is substantially faster than CMOS under both self-loading and constant loading.

Finally, a similar investigation has been carried out for  $I_{OFF} = 10$  pA/um at  $V_{DD} = 0.25$  V. The decrease of the supply voltage ensures a reduction of the ambipolar behaviour that allows to reach the LSTP  $I_{OFF}$  target. Results are summarized in Table I in terms of static power dissipation, TFET to CMOS speedup under self-loading [Speedup (Cin)] and constant loading [Speedup (CL)] conditions. Static power consumption is equal

for the two technologies as a design constraint, whereas other figures of merit are defined so that values greater than 1 indicate advantage of TFET over CMOS.

|                             | $I_{OFF} = 5 \text{ nA/um}$ $V_{DD} = 0.4 \text{ V}$ | $I_{OFF} = 5 \text{ nA/um}$ $V_{DD} = 0.25 \text{ V}$ | $I_{OFF} = 10 \text{ pA/um}$ $V_{DD} = 0.25 \text{ V}$ |

|-----------------------------|------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------------|

| P <sub>S</sub> (TFET, CMOS) | 14 pW                                                | 8.75 pW                                               | 0.0175 pW                                              |

| Speedup (C <sub>in</sub> )  | 0.55×                                                | 10×                                                   | 353×                                                   |

| Speedup (C <sub>L</sub> )   | 0.32×                                                | 7.45×                                                 | 105×                                                   |

Table I. Performance comparison of TFET and CMOS logic.

Table I clearly shows the potential of the TFET technology to perform substantially faster than a best-case CMOS implementation at 0.25 V supply voltage, for equal levels of static power consumption ( $P_S$ ) in line with the ITRS requirements.

### 5. Impact of Traps and Strain

Interface states may have a significant impact on the drain current, degrading both I<sub>ON</sub> and subthreshold slope [Passlack 10], [Lin 11]. In this respect, the achievement of low interface and border trap densities is one of the main technology challenges to be addressed [Pala 12]. For III–V-based TFETs, it is possible to boost the device performance, taking advantage of appropriate strain conditions [Visciarelli 16]. It was also shown that the trap energy levels remain unchanged in the presence of an external strain [Kim 11]. The detailed investigation of the effect of strain on InAs/GaSb heterojunction devices has been reported in [Visciarelli 17-SSE], where it was demonstrated that the application of an uniform biaxial tensile strain across the device cross section can provide the largest performance improvement. In principle, uniformly distributed strain across the whole structure could be achieved taking advantage of the lattice mismatches between the structure and the underlying substrate. Unfortunately, the application of a uniform strain along the whole device structure is especially challenging from the fabrication perspective. More reasonably, strain will be localized at the heterojunction because of lattice mismatch [Visciarelli 17-TED].

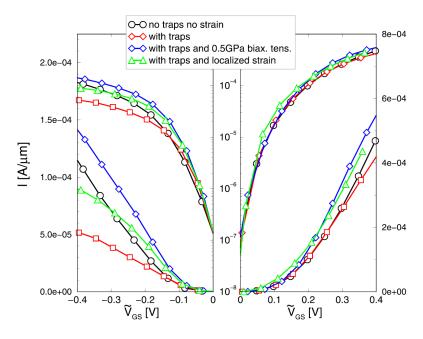

**Figure 6.**  $I_{DS}$  versus  $V_{GS}$  at  $|V_{DS}| = 0.4$  V without ITs (black circles), with traps (red squares), with uniform biaxial tensile strain of 0.5 GPa (blue diamonds), and localized strain (green triangles). (a) Tp. (b) Tn. Currents are normalized to the NW side, and the curves are  $V_G$ -shifted in order to have  $I_{ON} = 100$  nA/ $\mu$ m at  $V_{GS} = 0$  V.

In the absence of experimental data on strain maps in AlGaSb/InAs NW TFETs, we took advantage of process simulation results found in [Verreck 16] for a GaSb/InGaAs double-gate device, where the InGaAs region is assumed to be grown pseudomorphically on a relaxed GaSb. In order to reproduce this process simulation, we used a layer-dependent strain applied along the device cross section, with a strain map similar to that shown in [Verreck 16].

The I–V curves obtained considering traps and this localized strain caused by lattice mismatch are reported in Fig. 6. Curves are  $V_{GS}$ -shifted to match an  $I_{OFF} = 100$  nA/ $\mu$ m at  $V_{GS} = 0$  V. Currents with traps (red squares) are smaller than the ideal ones (black circles), but still steadily increasing with  $V_{GS}$ , indicating that a Fermi-pinning condition in the channel is not reached for the biases here considered. The current reduction is of  $\sim 60\%$  for Tp, and  $\sim 20\%$  for Tn.

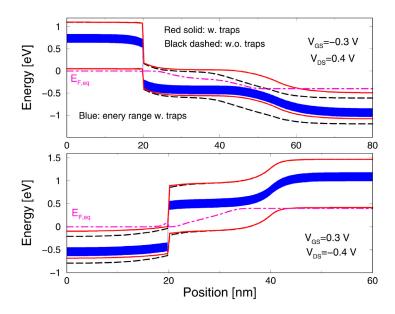

**Figure 7.** Conduction and valence subband profile for Tn (top) and Tp (bottom). VGS values are chosen in order to bias our devices in subthreshold. VDS = 0.4 V. Black dashed lines: without traps. Red solid lines: with traps. The energy interval where trap levels are located is highlighted (blue region). Magenta dashed curve: equivalent Fermi level.

For Tn, the current reduction caused by traps can be understood plotting the conduction and valence subband profiles [Fig. 7 (top)]. Trapped electrons in the channel lift up the conduction subband energy, hence increasing the tunneling distance. One positive side effect is the electric-field decrease at the channel/drain junction, responsible for ambipolar behavior. As for Tp, the situation is different, because the trapped charge affects the  $n^+$  source more than the channel/drain region. This is due to the fact that the trap distribution measured in [Wang 15] is of acceptor type [Fig. 7 (bottom)]. Indeed, for every applied voltage, traps in the channel and drain regions of Tn are always filled, since the trap energy levels are always below the equivalent Fermi level [see Fig. 6 (magenta dashed curve)]. The opposite happens for Tp, where the equivalent Fermi level is above the trap level in the source region, regardless of the applied gate voltage. With localized strain a performance improvement is obtained. For Tn, an  $I_{\rm ON} \sim 500~\mu A/\mu m$  higher than that exhibited by the fresh device is obtained, with SS = 32 mV/decade. For Tp, lattice mismatch is unable to completely recover the trap-induced  $I_{\rm ON}$  degradation, with  $I_{\rm ON} \sim 90~\mu A/\mu m$  and SS = 54 mV/decade. It is worth noting that for this localized strain, the bandgap is modified only near the heterojunction, leaving the band edges near the source/drain contacts unaltered (same degeneracy).

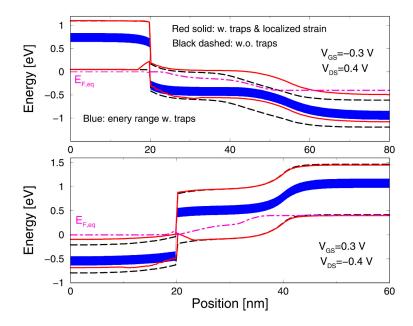

The subband profiles and trap energy level diagrams with this localized strain are reported in Fig. 8 at  $V_{GS} = -0.3V$  for Tn and at  $V_{GS} = 0.3V$  for Tp ( $|V_{DS}| = 0.4 V$ ), to be compared with Fig. 6 for the case with traps but without strain. The main point here is that, as a consequence of the bandgap decreasing, only at the

source/channel interface, the tunneling window increases, changing from a staggered- to a broken-gap heterojunction, whereas the source/drain regions near the contacts remain unchanged.

**Figure 8.** Conduction and valence subbands profile in subthreshold for TFETs Tn (top) and Tp (bottom). Black dashed lines: with no traps. Red solid lines: with traps and localized strain. The energy interval where trap levels are located (blue region) is reported as well. Magenta dashed curve: equivalent Fermi level.

#### 6. Conclusions

TFET technology has been reviewed in this paper as a potential alternative to conventional CMOS-based logic for near-future low-voltage/low-power applications. The proposed solutions integrate n- and p-type heterojunction TFETs with similar dimensions on a same InAs/Al<sub>0.05Ga0</sub>.95Sb platform. Full-quantum simulations have been employed to investigate static and dynamic performances of inverter blocks compatible with ITRS low-operating power requirements of the off-state leakage, i.e. 5nA/um. Results are compared with the best-case predictions for aggressively scaled CMOS logic based on multigate architectures. It is found that TFET implementations have potential to perform up to  $10\times$  and  $100\times$  faster than CMOS for  $I_{OFF} = 5nA/um$  and 10 pA/um, respectively, at very low supply voltage  $V_{DD} = 0.25 \text{ V}$ , for equal levels of static power dissipation. Afterwards, realistic trap energy distribution and strain conditions have been taken from the literature. However, it turns out that localized strain at the source/channel heterojunction caused by lattice mismatch is able to induce a performance enhancement for the n-type TFET with respect to the ideal device, even in the presence of traps. On the contrary, for the p-type one, a current degradation is still observed.

#### References

[AUTH 12] C. Auth, C. Allen, A. Blattner, D. Bergstrom, M. Brazier, M. Bost, et al., «A 22 nm high performance and low-power CMOS technology featuring fully-depleted tri-gate transistors, self-aligned contacts and high density MIM capacitors», in Proc. Symp. VLSI Technol., pp. 131–132, Jun. 2012.

[LU 14] H. Lu and A. Seabaugh, «Tunnel field-effect transistors: State-of-the-art», *IEEE J. Electron Device Soc.*, vol. 2, no. 4, pp. 44–49, Jul. 2014.

[IONESCU 11] A. M. Ionescu and H. Riel, «Tunnel field-effect transistors as energy efficient electronic switches», *Nature*, vol. 479, no. 7373, pp. 329–337, Nov. 2011.

[PAL 11] A. Pal, A. B. Sachid, H. Gossner, and V. R. Rao, «Insights into the design and optimization of tunnel-FET devices and circuits», *IEEE Trans. Electron Devices*, vol. 58, no. 4, pp. 1045–1053, Apr. 2011.

[MOOKERJEA 11] S. Mookerjea, R. Krishnan, S. Datta, and V. Narayanan, «Effective capacitance and drive current for tunnel FET TFET CV/I estimation», *IEEE Trans. Electron Devices*, vol. 56, no. 9, pp. 2092–2098, Sep. 2009.

- [PASSLACK 10] M. Passlack, R. Droopad, and G. Brammertz, «Suitability study of oxide/gallium arsenide interfaces for MOSFET applications», *IEEE Trans. Electron Devices*, vol. 57, no. 11, pp. 2944–2956, Nov. 2010.

- [LIN 11] L. Lin and J. Robertson, «Defect states at III–V semiconductor oxide interfaces», *Appl. Phys. Lett.*, vol. 98, no. 8, pp. 082903-1–082903-3, Feb. 2011.

- [PALA 12] M. G. Pala, D. Esseni, and F. Conzatti, «Impact of interface traps on the IV curves of InAs Tunnel-FETs and MOSFETs: A full quantum study», in *IEDM Tech. Dig.*, pp. 6.6.1–6.6.4, Dec. 2012.

- [BARAVELLI 14-I] E. Baravelli, E. Gnani, R. Grassi, A. Gnudi, S. Reggiani, G. Baccarani, «Optimization of n- and p-type TFETs integrated on the same InAs/Al<sub>x</sub>Ga<sub>1-x</sub>Sb technology platform», *IEEE Trans. Electron Devices*, vol. 61, no. 1, pp. 178 185, 2014.

- [BARAVELLI 14-II] E. Baravelli, E. Gnani, R. Grassi, A. Gnudi, S. Reggiani, G. Baccarani, «TFET Inverters With n-/p-Devices on the Same Technology Platform for Low-Voltage/Low-Power Applications», *IEEE Trans. Electron Devices*, vol. 61, no. 2, pp. 473 478, 2014.

- [LAKE 97] R. Lake, G. Klimeck, R. C. Bowen, and D. Jovanovic, «Single and multiband modeling of quantum electron transport through layered semiconductor devices», *J. Appl. Phys.*, vol. 81, no. 12, pp. 7845–7869, Jun. 1997.

- [BAHDER 90] T. B. Bahder, «Eight-band **k·p** model of strained zinc-blende crystals», *Phys. Rev. B, Condens. Matter*, vol. 41, no. 17, pp. 11992–12001, Feb. 1990.

- [BAHDER 93] T. Bahder, Erratum: «Eight-band k·p model of strained zinc-blende crystals», *Phys. Rev. B, Condens. Matter*, vol. 46, p. 9913, Oct. 1993.

- [VURGAFMANN 01] I. Vurgaftman and J. R. Meyer, «Band parameters for III–V compound semiconductors and their alloys», *J. Appl. Phys.*, vol. 89, pp. 5815–5875, Jun. 2001.

- [FOREMAN 01] B. A. Foreman, «Elimination of spurious solutions from eight-band **k·p** theory», *Phys. Rev. B, Condens. Matter*, vol. 56, pp. R12748–R12751, Jul. 2001.

- [VISCIARELLI 17-TED] M. Visciarelli, E. Gnani, A. Gnudi, S. Reggiani, G. Baccarani, «Impact of Traps and Strain on Optimized n- and p-Type TFETs Integrated on the Same InAs/AlGaSb Technology Platform», *IEEE Transactions on Electron Devices*, vol. 64, no. 8, pp. 3108 3113, 2017.

- [SINHA 12] S. Sinha, G. Yeric, V. Chandra, B. Cline, and Y. Cao, «Exploring sub-20 nm FinFET design with predictive technology models», *Proc.* 49th ACM/EDAC/IEEE DAC, pp. 283–288, 2012.

- [MOOKERJEA 09] S. Mookerjea, R. Krishnan, S. Datta, and V. Narayanan, «Effective capacitance and drive current for tunnel FET TFET CV/I estimation», *IEEE Trans. Electron Devices*, vol. 56, no. 9, pp. 2092–2098, Sep. 2009.

- [VISCIARELLI 16] M. Visciarelli, E. Gnani, A. Gnudi, S. Reggiani, and G. Baccarani, «Impact of strain on tunneling current and threshold voltage in III–V nanowire TFETs», *IEEE Electron Device Lett.*, vol. 37, no. 5, pp. 560–563, May 2016.

- [KIM 11] S. H. Kim et al., «Enhancement technologies and physical understanding of electron mobility in III–V n-MOSFETs with strain and MOS interface buffer engineering», *IEDM Tech. Dig.*, pp. 311–314, Dec. 2011.

- [VISCIARELLI 17-SSE] M. Visciarelli, E. Gnani, A. Gnudi, S. Reggiani, and G. Baccarani, «Design guidelines for GaSb/InAs TFET exploiting strain and device size», *Solid-State Electron.*, vol. 129, pp. 157–162, Mar. 2017.

- [VERRECK 16] D. Verreck et al., «Non-uniform strain in lattice-mismatched heterostructure tunnel field-effect transistors», *Proc. 46th Eur. Solid-State Device Res. Conf. (ESSDERC)*, pp. 412–415, Sep. 2016.

- [WANG 15] S.-W. Wang et al., «Field-effect mobility of InAs surface channel nMOSFET with low D<sub>it</sub> scaled gate-stack», *IEEE Trans. Electron Devices*, vol. 62, no. 8, pp. 2429–2436, Aug. 2015.